The finFETs might enable engineers to sidestep a problem threatening to derail the electronics industry. New technologies will be needed for industry to keep pace with Moore's law, an unofficial rule stating that the number of transistors on a computer chip doubles about every 18 months, resulting in rapid progress in computers and telecommunications. Doubling the number of devices that can fit on a computer chip translates into a similar increase in performance. However, it is becoming increasingly difficult to continue shrinking electronic devices made of conventional silicon-based semiconductors.

In addition to making smaller transistors possible, finFETs also might conduct electrons at least five times faster than conventional silicon transistors, called MOSFETs, or metal-oxide-semiconductor field-effect transistors.

"The potential increase in speed is very important," Ye said. "The finFETs could enable industry to not only create smaller devices, but also much faster computer processors."

Transistors contain critical components called gates, which enable the devices to switch on and off and to direct the flow of electrical current. In today's chips, the length of these gates is about 45 nanometers, or billionths of a meter.

The semiconductor industry plans to reduce the gate length to 22 nanometers by 2015. However, further size reductions and boosts in speed are likely not possible using silicon, meaning new designs and materials will be needed to continue progress.

Indium-gallium-arsenide is among several promising semiconductor alloys being studied to replace silicon. Such alloys are called III-V materials because they combine elements from the third and fifth groups of the periodical table.

Creating smaller transistors also will require finding a new type of insulating layer essential for the devices to switch off. As gate lengths are made smaller than 22 nanometers, the silicon dioxide insulator used in conventional transistors fails to perform properly and is said to "leak" electrical charge.

One potential solution to this leaking problem is to replace silicon dioxide with materials that have a higher insulating value, or "dielectric constant," such as hafnium dioxide or aluminum oxide.

The Purdue research team has done so, creating finFETs that incorporate the indium-gallium-arsenide fin with a so-called "high-k" insulator. Previous attempts to use indium-galliumarsenide finFETs to make devices have failed because too much current leaks from the circuit.

The researchers are the first to "grow" hafnium dioxide onto finFETs made of a III-V material using atomic layer deposition. The approach could make it possible to create transistors using the thinnest insulating layers possible - only a single atomic layer thick.

The finlike design is critical to preventing current leakage, in part because the vertical structure can be surrounded by an insulator, whereas a flat device has the insulator on one side only.

The work is funded by the National Science Foundation and the Semiconductor Research Consortium and is based at the Birck Nanotechnology Center in Purdue's Discovery Park.

Writer: Emil Venere, 765-494-4709, venere@purdue.edu

Source: Peide Ye, 765-494-7611, vep@purdue.edu

Purdue News Service: (765) 494-2096; purduenews@purdue.edu

Note to Journalists: An electronic copy of one of the papers is available from Emil Venere, 765-494-4709, <u>venere@purdue.edu</u>

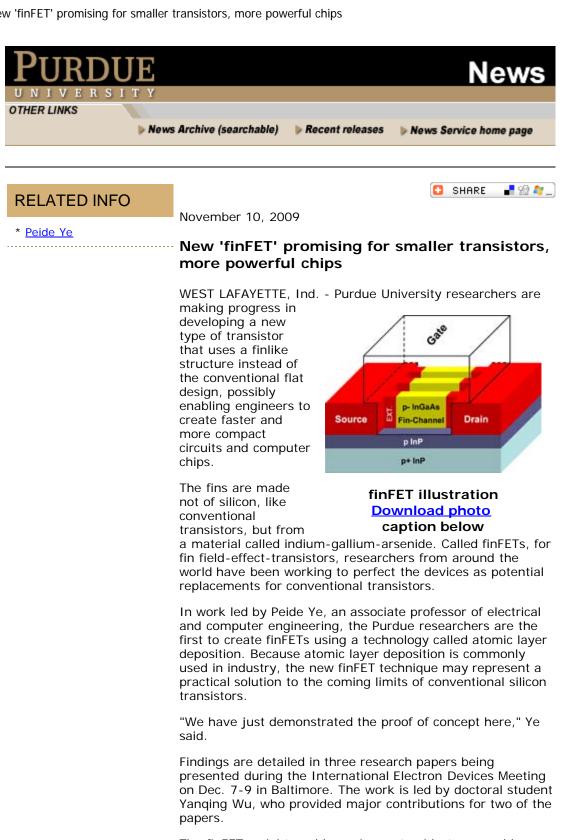

IMAGE CAPTION:

Researchers are making progress in developing new types of transistors, called finFETs, which use a finlike structure instead of the conventional flat design, possibly enabling engineers to create faster and more compact circuits and computer chips. The fins are made not of silicon, but from a material called indium-gallium-arsenide, as shown in this illustration. (Birck Nanotechnology Center, Purdue University)

A publication-quality image is available at <a href="http://news.uns.purdue.edu/images/+2009/ye-finfets.jpg">http://news.uns.purdue.edu/images/+2009/ye-finfets.jpg</a>

## ABSTRACT

## First Experimental Demonstration of 100 nm Inversion-mode InGaAs FinFET through Damage-free Sidewall Etching

Y.Q. Wu, R.S. Wang, T. Shen, J.J. Gu and P. D. Ye

School of Electrical and Computer Engineering, Birck Nanotechnology Center Purdue University

The first well-behaved inversion-mode InGaAs FinFET with gate length down to 100 nm with ALD Al2O3 as gate dielectric has been demonstrated. Using a damage-free sidewall etching method, FinFETs with Lch down to 100 nm and WFin down to 40 nm are fabricated and characterized. In contrast to the severe short-channel effect (SCE) of the planar InGaAs MOSFETs at similar gate lengths, finFETs have much better electro-static control and show improved S.S., DIBL and VT roll-off and less degradation at elevated temperatures. The SCE of III-V MOSFETs is greatly improved by the 3D structure design. The more accurate Dit estimation from the S.S. is also presented.

To the News Service home page

🖸 SHARE 🛛 📲 😭 🦓 ...